Käteviä ADC- ja DAC-muuntimia IoT-aikakaudelle30.10.2019

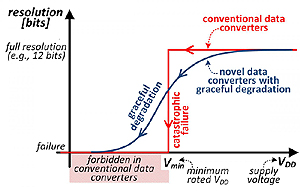

Singaporen kansallisen yliopiston (NUS) Green IC -työryhmä on kehittänyt uudenlaisien digitaali-analogia (DAC) ja analogia-digitaali -muuntimien (ADC) luokan. Niillä on täysin digitaalinen arkkitehtuuri, joten ne pystytään suunnittelemaan täysin automatisoidulla digitaalisella suunnittelumenetelmällä. Verrattuna perinteisiin analogisiin arkkitehtuureihin ja metodologioihin, näiden uusien anturien rajapintojen suunnitteluaika on lyhentynyt kuukausista tunteihin. Suunnittelutyön dramaattinen vähentäminen on erittäin hyödyllistä esimerkiksi esineiden Internetin (IoT) antureissa. Uudella datamuuntimen arkkitehtuurilla on myös erittäin alhainen monimutkaisuus, mikä vähentää piipinta-alaa ja siten valmistuskustannuksia vähintään 30-kertaisesti perinteisiin suunnitelmiin verrattuna. Näillä uusilla datamuuntajilla on myös ennennäkemätön kyky heikentää signaalin uskollisuutta sulavasti, kun sen syöttöjännite tai kellotaajuus kokee suuria vaihteluita. Tällaiset vaihtelut ovat yleisiä energiaa keräävillä IoT-antureilla, koska ympäristöstä kerätty energia on varsin epätasaista. Tämä puolestaan mahdollistaa anturien signaalien jatkuvan seurannan myös epäsuotuisissa energian keruun olosuhteissa ja ilman jännitesäätöä. Perinteiset datamuuntimet kärsivät katastrofaalisesta resoluution heikkenemisestä, kun syöttöjännite on alle nimellisarvon tai taajuus ylittää suurimman nimellisarvonsa. Tällöin tarvitaan tehosyöppöjä piirejä jännitteen ja taajuuden hallintaan. "Tutkimuksemme muuttaa datamuuntimien perinteisesti analogisen ja enimmäkseen manuaalisen suunnittelun täysin automatisoiduksi digitaalisuunnitteluksi, vähentämällä piipinta-alaa suuruusluokalla ja suunnitteluaikaa kahdella suuruusluokalla, jolloin puolijohdeyritykset voivat olla kustannuskilpailukykyisiä, samalla kun pääsevät markkinoille nopeammin", toteaa ryhmän johtaja apulaisprofessori Massimo Alioto. NUS-tiimi esitteli konseptin useilla piisiruilla ja toteuttivat sekä DAC:t että ADC:t erittäin pienellä alan käytöllä. Esimerkiksi 12-bittinen DAC valmistettiin 40 nm:n standardilla CMOS-tekniikalla, mikä antaa vielä runsaasti tilaa skaalaukselle. Samalla uuden konseptin on osoitettu mahdollistavan 16-bittiset datamuuntimet. Tiimin jäsen tohtori Orazio Aiello sanoi: "Tiimimme on ottanut käyttöön uuden suunnittelumallin, joka vie meidät lähemmäksi lopullista näkemystä edullisista, teknologisesti skaalautuvista ja erittäin pienikokoisista Internet-laitteista." Parhaillaan tutkijat paneutuvat useisiin vastaavaan idean toteuttamiseen erilaisiin alajärjestelmiin, kuten vahvistimiin, oskillaattoreihin, jännite- ja virtareferensseihin yms. Tutkimus tehtiin yhteistyössä apulaisprofessori Paolo Crovettin kanssa Politecnico di Torinosta Italiasta ja sitä tukevat Singaporen opetusministeriö ja EU-komissio. |

| 24.04.2024 | Akku ja superkonkka yhteen soppii |

| 23.04.2024 | Kaareva datalinkki esteitä ohittamaan |

| 22.04.2024 | Kvanttimateriaali lupaa uutta puhtia aurinkokennoille |

| 21.04.2024 | Läpimurto lupaa turvallista kvanttilaskentaa kotona |

| 20.04.2024 | Yksi atomikerros kultaa ja molekyylikorjaaja |

| 19.04.2024 | Uusia ja yllättäviä topologiota |

| 18.04.2024 | Kvanttivalo syntyy renkaassa ja lähtee kiertueelle |

| 17.04.2024 | Fononit ja magnonit kaveraavat |

| 16.04.2024 | E-nenälle ihmisen tasoinen hajuaisti |

| 15.04.2024 | Valo valtaa alaa magnetismissa |

|

Siirry arkistoon » |

Katastrofinen epäonnistuminen korvataan kätevällä resoluution heikkenemisellä NUS-tutkijoiden kehittämien uusien perinteisten datamuuntimien luokassa.

Katastrofinen epäonnistuminen korvataan kätevällä resoluution heikkenemisellä NUS-tutkijoiden kehittämien uusien perinteisten datamuuntimien luokassa.